1.完整项目描述和程序获取

>面包多安全交易平台:https://mbd.pub/o/bread/YZWTmJ1rbA==

>如果链接失效,可以直接打开本站店铺搜索相关店铺:

>如果链接失效,程序调试报错或者项目合作也可以加微信或者QQ联系。

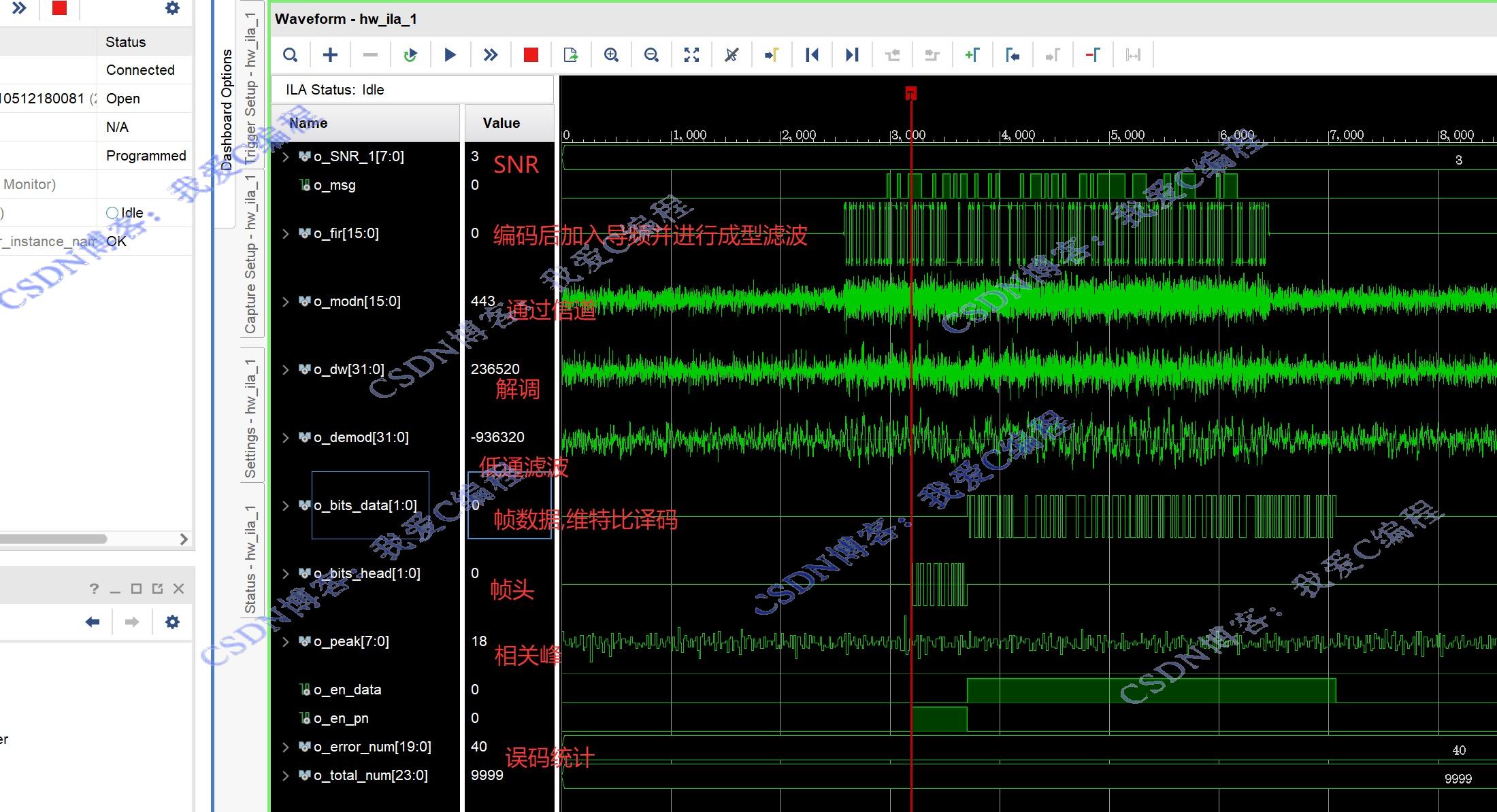

2.部分仿真图预览

3.算法概述

基于二进制相移键控(BPSK)、卷积编码及 Viterbi 译码的通信系统,是数字通信领域中典型的抗噪声传输方案。该系统通过卷积编码引入冗余度以抵抗信道干扰,利用Viterbi 算法实现最大似然译码,结合BPSK 调制提升频带利用率,并通过帧同步技术确保收发端数据对齐。其核心流程包括:信源→卷积编码→帧同步头插入→BPSK 调制→信道传输→BPSK解调→帧同步→Viterbi 译码→信源。

4.部分源码

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2025/05/23 12:59:21

// Design Name:

// Module Name: tops_hdw

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module tops_hdw(

input i_clk,

input i_rst,

output reg [3:0] led

);

wire signed[1:0]o_en;

wire o_msg;

wire dat_clk;

wire dat_2clk;

signal signal_u(

.i_clk (i_clk),

.i_rst (~i_rst),

.o_en(o_en),

.o_bits(o_msg),

.dat_clk(dat_clk),

.dat_2clk(dat_2clk)

);

//设置SNR

wire signed[7:0]o_SNR;

vio_0 your_instance_name (

.clk(i_clk), // input wire clk

.probe_out0(o_SNR) // output wire [7 : 0] probe_out0

);

wire [1:0]o_enc;

wire o_encs;

wire signed[15:0]o_fir;

wire signed[15:0]o_mod;

wire signed[15:0]o_modn;

wire signed[31:0]o_dw;

wire signed[31:0]o_demod ;

wire signed[31:0]o_error_num;

wire signed[31:0]o_total_num;

wire [1:0]o_bits_data;

wire [1:0]o_bits_head;

wire [7:0]o_peak;

wire o_en_data;

wire o_en_pn;

wire o_frame_start;

BPSK uut(

.i_clk(i_clk),

.i_clkdx(dat_clk),

.i_clkd2x(dat_2clk),

.i_rst(~i_rst),

.i_en (o_en),

.i_bits(o_msg),

.i_SNR(o_SNR),

.o_enc(o_enc),

.o_encs(o_encs),

.o_fir(o_fir),

.o_mod(o_mod),

.o_modn(o_modn),

.o_dw(o_dw),

.o_demod(o_demod),

.o_bits (),

.o_bits_data (o_bits_data),

.o_bits_head (o_bits_head),

.o_peak (o_peak),

.o_en_data (o_en_data),

.o_en_pn (o_en_pn),

.o_frame_start (o_frame_start),

.o_error_num (o_error_num),

.o_total_num (o_total_num)

);

//ila篇内测试分析模块

ila_0 ila_u (

.clk(i_clk), // input wire clk

.probe0({

o_msg,o_SNR,//10

o_fir,o_modn,o_dw,o_demod,//64

o_bits_data,o_bits_head,o_peak,o_en_data,o_en_pn,//14

o_error_num[19:0],o_total_num[23:0]//44

})

);

endmodule

0sj_077m

---