1.完整项目描述和程序获取

>面包多安全交易平台:https://mbd.pub/o/bread/ZJ6amJ9s

>如果链接失效,可以直接打开本站店铺搜索相关店铺:

>如果链接失效,程序调试报错或者项目合作也可以加微信或者QQ联系。

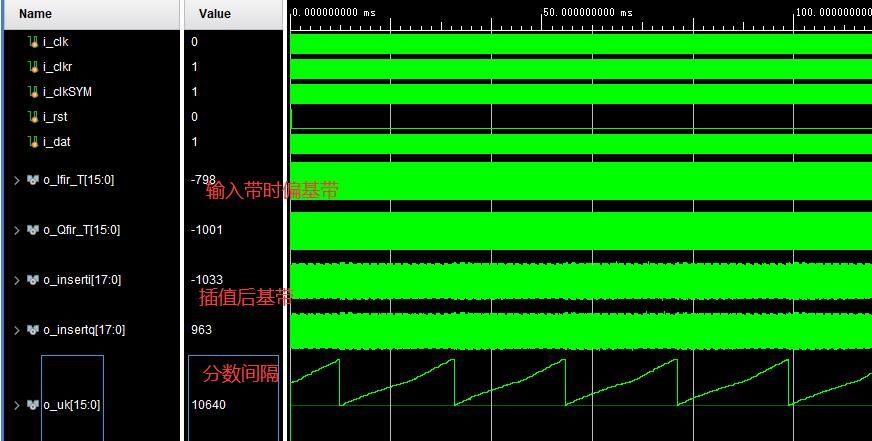

2.部分仿真图预览

3.算法概述

Gardner算法是一种非判决指向方法,其基本思想是提取相邻码元最佳采样点的幅度和极性变化信息,以及相邻码元过渡点是否为零这一信息,从而从采样信号中提取出定时误差。在系统设计中,Gardner锁相环位于Costas载波同步锁相环之后,主要由四部分组成:内插器、时钟误差提取模块、环路滤波器以及控制器模块。

4.部分源码

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2023/09/27 02:16:25

// Design Name:

// Module Name: TEST

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module TEST();

reg i_clk;

reg i_clkr;

reg i_clkSYM;

reg i_rst;

reg i_dat;

wire signed[15:0]o_Ifir_T;

wire signed[15:0]o_Qfir_T;

//QPSK调制

Tqpsk Tqpsku(

.i_clk (i_clk),

.i_clkSYM(i_clkSYM),

.i_rst (i_rst),

.i_dat(i_dat),

.o_Ifir (o_Ifir_T),

.o_Qfir (o_Qfir_T)

);

wire signed [17:0] o_inserti; //插值I支路数据

wire signed [17:0] o_insertq; //插值Q支路数据

wire signed [15:0] o_uk; //插值间隔输出

wire o_syn_clock; //位同步脉冲/1MHz

Gardner_tops Gardner_topsuut(

.i_clk (i_clkr),

.i_rst (i_rst),

.i_basei (o_Ifir_T),

.i_baseq (o_Qfir_T),

.o_inserti (o_inserti),

.o_insertq (o_insertq),

.o_syn_clock (o_syn_clock),

.o_uk (o_uk)

);

initial

begin

i_clk = 1'b1;

i_clkr= 1'b1;

i_clkSYM=1'b1;

i_rst = 1'b1;

#160000

i_rst = 1'b0;

end

always #1000 i_clk=~i_clk;

always #1005 i_clkr=~i_clkr;

always #8000 i_clkSYM=~i_clkSYM;

initial

begin

i_dat = 1'b0;

#144000

repeat(1000)

begin

#16000 i_dat = 1'b1;

#16000 i_dat = 1'b1;

#16000 i_dat = 1'b0;

#16000 i_dat = 1'b0;

#16000 i_dat = 1'b0;

#16000 i_dat = 1'b1;

#16000 i_dat = 1'b0;

#16000 i_dat = 1'b1;

#16000 i_dat = 1'b1;

#16000 i_dat = 1'b0;

#16000 i_dat = 1'b0;

#16000 i_dat = 1'b0;

#16000 i_dat = 1'b0;

#16000 i_dat = 1'b0;

#16000 i_dat = 1'b0;

#16000 i_dat = 1'b0;

#16000 i_dat = 1'b0;

#16000 i_dat = 1'b0;

#16000 i_dat = 1'b1;

#16000 i_dat = 1'b1;

#16000 i_dat = 1'b1;

#16000 i_dat = 1'b0;

#16000 i_dat = 1'b0;

#16000 i_dat = 1'b1;

#16000 i_dat = 1'b0;

#16000 i_dat = 1'b0;

#16000 i_dat = 1'b1;

#16000 i_dat = 1'b1;

#16000 i_dat = 1'b0;

#16000 i_dat = 1'b0;

#16000 i_dat = 1'b1;

#16000 i_dat = 1'b1;

#16000 i_dat = 1'b0;

#16000 i_dat = 1'b0;

#16000 i_dat = 1'b0;

#16000 i_dat = 1'b1;

#16000 i_dat = 1'b0;

#16000 i_dat = 1'b1;

#16000 i_dat = 1'b0;

#16000 i_dat = 1'b0;

#16000 i_dat = 1'b1;

#16000 i_dat = 1'b1;

#16000 i_dat = 1'b0;

#16000 i_dat = 1'b0;

#16000 i_dat = 1'b0;

#16000 i_dat = 1'b1;

#16000 i_dat = 1'b1;

#16000 i_dat = 1'b1;

#16000 i_dat = 1'b1;

#16000 i_dat = 1'b0;

#16000 i_dat = 1'b1;

#16000 i_dat = 1'b0;

#16000 i_dat = 1'b1;

#16000 i_dat = 1'b1;

#16000 i_dat = 1'b0;

#16000 i_dat = 1'b0;

#16000 i_dat = 1'b0;

#16000 i_dat = 1'b0;

end

$stop();

end

endmodule

---