1.完整项目描述和程序获取

>面包多安全交易平台:https://mbd.pub/o/bread/ZJiWmJly

>如果链接失效,可以直接打开本站店铺搜索相关店铺:

>如果链接失效,程序调试报错或者项目合作也可以加微信或者QQ联系。

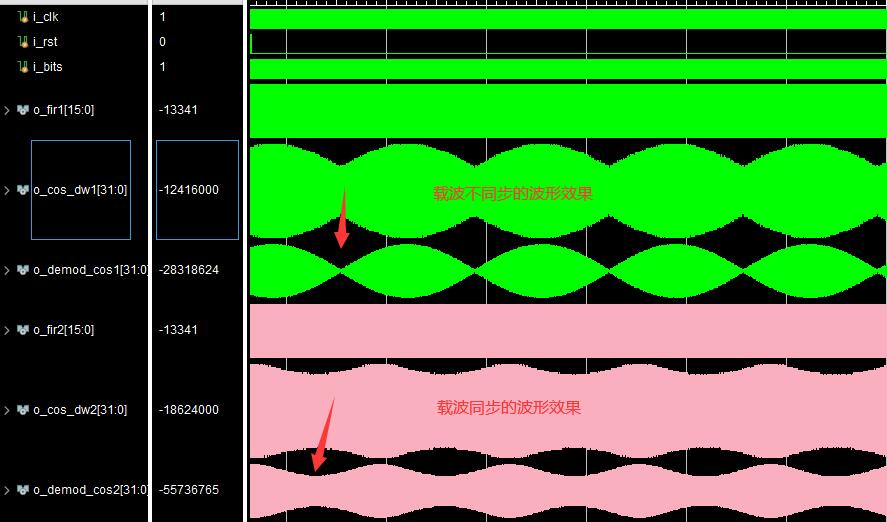

2.部分仿真图预览

3.算法概述

载波恢复的主要作用是通过接收信号中的载波信息来恢复出发送信号中的载波频率和相位,从而实现信号的相干解调。常见的载波恢复方法包括PLL(Phase-Locked Loop)和Costas环等。相位解调的主要作用是将接收信号的相位信息转化为数字信号,从而实现数字信号的解调。常见的相位解调方法包括差分相位解调和非差分相位解调等。

4.部分源码

.............................................................

//调制端

wire[1:0] o_nz=(i_bits == 1'b1)?2'b01:2'b11;

wire[31:0]m_fir;

fiter_rrc uut(

.i_clk (i_clk),

.i_rst (i_rst),

.i_dat ({o_nz[1],o_nz[1],o_nz[1],o_nz[1],o_nz[1],o_nz[1],o_nz,8'd0}),

.o_demod(m_fir)

);

assign o_fir=m_fir[27:12];

wire[15:0]m_carrier;

dds_compiler_0 uut2(

.aclk (i_clk),

.aresetn (~i_rst),

.s_axis_config_tvalid(1'b1),

.s_axis_config_tdata(32'd100000000 + 32'd20000),//加入频偏<=20000

.m_axis_data_tvalid(),

.m_axis_data_tdata(m_carrier),

.m_axis_phase_tvalid(),

.m_axis_phase_tdata()

);

assign o_carrier={m_carrier[7:0],8'd0};

always @(posedge i_clk or posedge i_rst)

begin

if(i_rst)

begin

o_mod <= 32'd0;

end

else begin

o_mod <= $signed(o_carrier)*$signed(o_fir);

end

end

/

//解调端 ,考虑载波同步

//NCO

wire signed[31:0]o_K;

wire[15:0]m_carrier_local;

dds_compiler_0 uut3(

.aclk (i_clk),

.aresetn (~i_rst),

.s_axis_config_tvalid(1'b1),

.s_axis_config_tdata(32'd100000000 + i_sel*o_K),

.m_axis_data_tvalid(),

.m_axis_data_tdata(m_carrier_local),

.m_axis_phase_tvalid(),

.m_axis_phase_tdata()

);

wire signed[15:0] o_sin_local={m_carrier_local[15:8],8'd0};

wire signed[15:0] o_cos_local={m_carrier_local[7:0],8'd0};

//下变频

..............................................................

//匹配滤波

wire signed[31:0] o_demod_sin;

fiter_rrc uut4(

.i_clk (i_clk),

.i_rst (i_rst),

.i_dat (o_sin_dw[31:16]),

.o_demod(o_demod_sin)

);

fiter_rrc uut5(

.i_clk (i_clk),

.i_rst (i_rst),

.i_dat (o_cos_dw[31:16]),

.o_demod(o_demod_cos)

);

//鉴相器

..............................................

//环路滤波

lpf lpfu(

.i_clk (i_clk),

.i_rst (i_rst),

.i_din (o_mods),

.o_K (o_K),

.o_Ks ()

);

endmodule

00_002m